独習

OpenCL

基礎演習

Atlas-SoC

編

独習

OpenCL

基礎演習

Atlas-SoC

編

目次

...3 1.

演習環境 ... 3 1-1.

“Atlas-SoC” ... 4 1-2.

付属 内容 ... 5 1-3.

ン ...6 2.

ン ... 6 2-1.

2-1-1. 一般的 ン ... 6 2-1-2. SDK for OpenCL 実装 ... 6 開発 ... 7 2-2.

事前準備 ...8 3.

Quartus Prime 開発ソ ン ... 8 3-1.

SoC EDS ン ... 8 3-2.

SDK for OpenCL ン ... 8 3-3.

v15.1 用 Atlas-SoC ン 追 ... 9

3-4.

Windows 環境変数 確認 設定 ... 9 3-5.

演習 出 ... 10 3-6.

そ 他 ン ... 10 3-7.

Atlas-SoC PC 接続 ... 10 3-8.

PC側ネ ワ 設定 ...11 3-9.

UART 接続確認 Linux 起動 ... 12 3-10.

Ethernet 接続確認 ... 13 3-11.

演習 ...14 4.

ン ン 起動 ... 14 4-1.

ネ ン ... 15 4-2.

ョン ン ... 16 4-3.

転送 ... 17 4-4.

OpenCL 実行 ... 18 4-5.

1.

資料 SoC 利用 OpenCL™ FPGA 高位合成 行う方法 解

提供 SDK for OpenCL 使用 演習 体験 迅速 簡単 セ

構築 方法 理解 演習 単純 配列 算 処理 OpenCL 実装

演習環境 1-1.

本演習 記 開発環境 使用

表1-1.1 資料 明 使用 い 主 開発環境

項番 項目 内容

1 PC Microsoft® Windows® 7 Professional sp1 64 bit 搭載 64 bit ン

2 Quartus®

Prime 開発ソ

SoC FPGA 開発

ソ 開発 必要 ン 生成 行い

本 明書 Quartus Prime 開発ソ ョン v15.1 使用 い

■ Quartus Prime 開発ソ ョン v15.1

http://dl.altera.com/15.1/?edition=lite

3 SoC EDS ARM® DS-5TM Altera Edition

SoC FPGA ソ 開発

ョン ソ ン

本 明書 SoC EDS v15.1.1 使用 い

■ SoC ン ン v15.1.1

http://dl.altera.com/soceds/15.1.1/?edition=standard

4 SDK for

OpenCL

FPGA OpenCL ソ 開発

OpenCL ネ ン 実行

本 明書 SDK for OpenCL v15.1 使用 い

■ SDK for OpenCL v15.1

http://dl.altera.com/opencl/15.1/?edition=standard

5 Atlas-SoC 本資料 明 使用 Cyclone® V SoC 搭載

Terasic Atlas-SoC

■ Atlas-SoC

http://rocketboards.org/foswiki/view/Documentation/AtlasSoCDevelopmentPlatform

6 演習 ン 本資料 演習 使用 Atlas-SoC 動作 単純 配列 算 処理

OpenCL 実装

ョン 入力 確保 乱数 格納 行い ネ FPGA

演算 算値 正 い 比較

Atlas-SoC 1-2.

Cyclone V SoC 搭載 い

図1-2.1 Atlas-SoC

(1) Atlas-SoC 設定 確認

図1-2.2 SW10 設定

表1-2.1 SW10 設定表

ン 信号 内容 設定

SW10-1 MSEL 0

ン FPGA ン ュ ョン方

法 選択 使用

ON

SW10-2 MSEL 1 OFF

SW10-3 MSEL 2 ON

SW10-4 MSEL 3 OFF

SW10-5 MSEL 4 ON

付属 内容 1-3.

独習 OpenCL 基礎演習 Atlas-SoC 版 付属

Self-study_Altera_OpenCL_basic_v15.1 for Atlas-Soc.zip 解凍 以 含 い

■ BSP_Atlas ン

board

c5soc_atlas

arm32 : ョン用 等

c5soc_atlas_sharedonly : ン driver

board_env.xml share

■ Lab 演習

Altera-SoCFPGA-OpenCL-vectorAdd.tar.gz ■ SD_Image OpenCL 用 SD

atlas_opencl_sdimage_v1511_r3.tgz

ン

2.

SDK for OpenCL ン ARM Cortex-A9 セ ANSI C

言語 あ OpenCL C 記述 ソ 関数 ネ FPGA ン セ

合成 実行

章 OpenCL 開発 け ネ FPGA ンへ 合成 ン 理解

ン 2-1.

2-1-1.一般的 ン

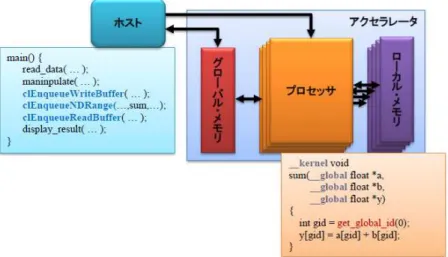

OpenCL 一般的 ン 図 示

確保 セ 処理 準備 セ 制御 移

セ そ 処理 後 再び 制御 戻 処理 完了 通知

図 2-1-1.1 一般的 ン

2-1-2. SDK for OpenCL 実装

SDK for OpenCL ARM Cortex-A9 セ

DDR3-SDRAM セ FPGA FPGA 内 RAM 実装

開発 2-2.

OpenCL 記述 OpenCL FPGA 実装 部分 記述 ネ

そ ネ 制御 記述

ネ OpenCL C 記述 そ セ 動作 最

初 ネ 標準 C 言語 記述 正 く動作 確認 OpenCL C 変換

推奨

続い ネ FPGA ン 合成 ン .aocx Altera Offline Compiler eXecutable

file 生成 Linux 転送

PC ン 環境 実行可能 ョン ン

転送

ョン 実行 生成 .aocx FPGA ン ュ ョン ネ

記述 機能 等 処理 FPGA 使用 実行

図 2-2.1 SDK for OpenCL 開発

事前準備

3.

章 演習 実施 必要 機材 確認 ン

後述 既 ン 済 場合 新 ン 必要 あ 飛

ば く い

Quartus Prime 開発ソ ン

3-1.

(1) 今回 Quartus Prime v15.1 Windows 版 ン ン

償 セン 必要 ン ョン 無償 ョン 構い

(2) Windows 環境変数 開い LM_LICENSE_FILE 追 OpenCL 評価用 セン

設定

[注意事項]

OpenCL 評価用 セン 別途 客様担当 代理店 問い合わ く い

図 3-1.1 LM_LICENSE_FILE 環境変数 設定

SoC EDS ン

3-2.

SoC EDS v15.1.1 Windows 版 ン ン

SDK for OpenCL ン

3-3.

SDK for OpenCL v15.1 Windows 版 ン ン

OK

OK

LM_LICENSE_FILE 設定 い 確認

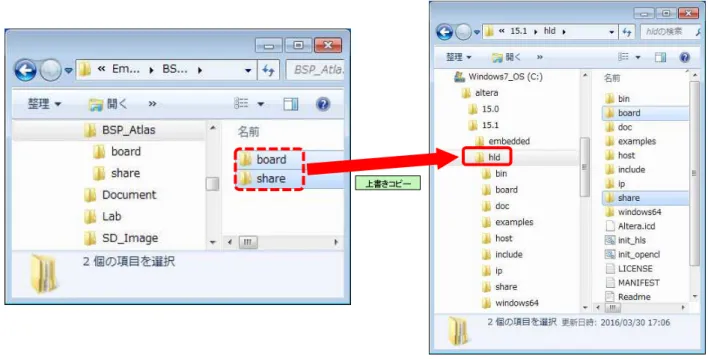

v15.1 用 Atlas-SoC ン 追 3-4.

付属 BSP_Atlas 中身 board share SDK for OpenCL v15.1 ン

例: C:¥altera¥15.1¥hld 書 く い

図 3-4.1 Atlas-SoC ン 追

board c5soc_atlas 追 share¥models¥dm

5csema4u23c6n_dm.xml 追

Windows 環境変数 確認 設定

3-5.

Windows 環境変数 開い 記 変数 追 く い

(1) 以 環境変数 在 正 い値 設定 い 確認

● 変数: ALTERAOCLSDKROOT

値: 例: C:\altera\15.1\hld

● 変数: QUARTUS_ROOTDIR

値: 例: C:\altera\15.1\quartus

(2) 以 環境変数 追

● 変数: AOCL_BOARD_PACKAGE_ROOT

値: %ALTERAOCLSDKROOT%\board\c5soc_atlas

● 変数: PATH

値: %QUARTUS_ROOTDIR%\bin64;%ALTERAOCLSDKROOT%\windows64\bin

演習 出 3-6.

付属 内 Lab 中 あ Altera-SoCFPGA-OpenCL-vectorAdd.tar.gz PC

任意 ワ 例 C:¥Work 解凍

解凍 ン ン ン ン 実行

Windows SoC EDS ン 例 C:¥altera¥15.1¥embedded 開

そ あ Embedded_Command_Shell.bat ン ン 起動 以

ン Altera-SoCFPGA-OpenCL-vectorAdd.tar.gz 解凍

$ cd "C:\Work" ↲

$ tar -xzf Altera-SoCFPGA-OpenCL-vectorAdd.tar.gz ↲

[注意事項]

&解凍先 や日本語 全角文 無い う注意 く い

そ 他 ン

3-7.

UART ソ ン 本資料 Tera Term 使用 い 機能的 等

あ ば別 使 構い

ン や ン 別途 作成者 関連 情報 参考

く い

Atlas-SoC PC 接続

3-8.

PC Atlas-SoC 接続 microSD 挿入 電源 入 く い

図 3-8.1 Atlas-SoC PC 接続

[注意事項]

付属 内 SD_Image

atlas_opencl_sdimage_v1511_r3.tgz

あ ン ン tar -xzf ン 解凍 ソ

Win32DiskImager 使用 microSD 書 込

AC

PC ( ン)

USB

ネ

ETHERNET UART

microSD Card

Atlas-SoC

USBBLASTER II

PC側ネ ワ 設定 3-9.

Atlas-SoC PC Ethernet 接続 設定 行い

(1) Windows ュ ン ネ 選択 ネ ワ 共 セン

(2) 設定 変更 開い 接続 選択 右 選択

(3) 表示 ン ネ ョン 4 (TCP/IPv4) 選択

ン

(4) 次 IP 使う 入 IP ネ 任意 入

力 例 IP : 192.168.1.31、 ネ : 255.255.255.0 設定

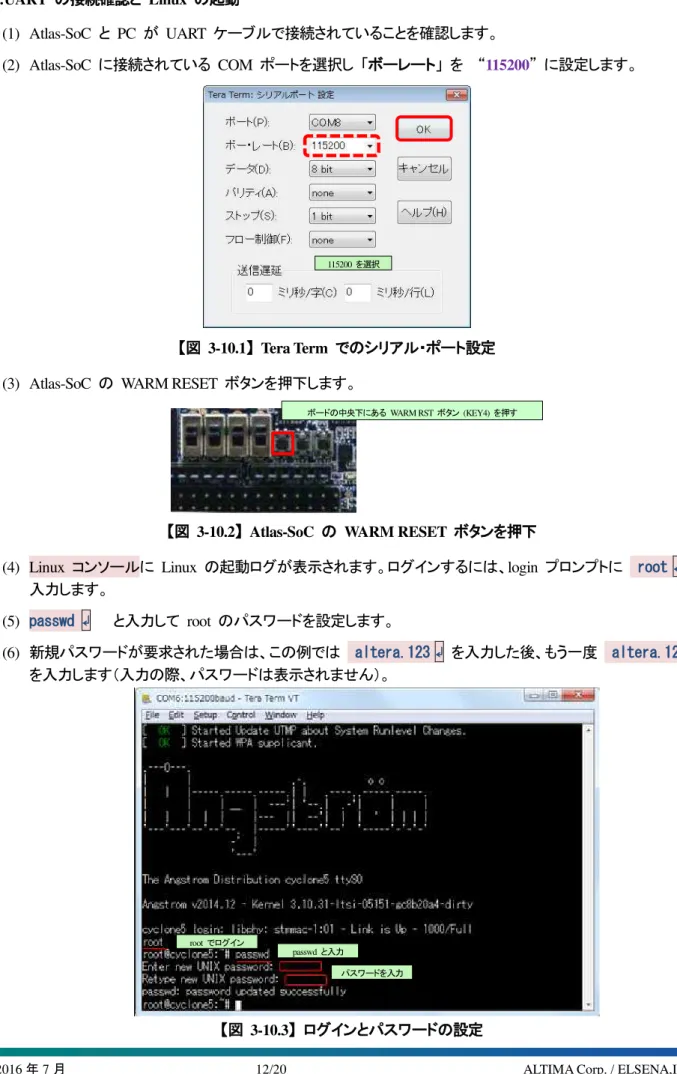

UART 接続確認 Linux 起動 3-10.

(1) Atlas-SoC PC UART 接続 い 確認

(2) Atlas-SoC 接続 い COM 選択 115200 設定

図 3-10.1 Tera Term 設定

(3) Atlas-SoC WARM RESET ン

図 3-10.2 Atlas-SoC WARM RESET ン

(4) Linux ンソ Linux 起動 表示 ン login ン root ↲

入力

(5) passwd ↲ 入力 root ワ 設定

(6) 新規 ワ 要求 場合 例 altera.123 ↲ 入力 後 う一度 altera.123 ↲

入力 入力 際 ワ 表示

115200 選択

中央 あ WARM RST ン (KEY4)

root ン

ワ 入力

Ethernet 接続確認 3-11.

Atlas-SoC PC Ethernet 接続 い 確認

(1) Linux ンソ 任意 IP 設定 例 192.168.1.30 設定 以

う 入力 く い

# ifconfig eth0 192.168.1.30 ↲

(2) 続い Linux び PC 双方 Ping 送 正 く接続 い 確認 そ 際

Ping 通 い場合 Windows 設定 解除 く い

図 3-11.1 Ethernet 接続確認 Linux ンソ 実行

演習

4.

演習 前述 3-6. 演習 出 解凍 Altera-SoCFPGA-OpenCL-vectorAdd 使用

単純 配列 算 処理 OpenCL 実装

ョン 入力 確保 乱数 格納 行い ネ FPGA 演算

算値 正 い 比較

ン ン 起動

4-1.

後ほ 実行 ネ ン ョン ン ン

ン ン ン 実行

(1) Windows SoC EDS ン 例 C:¥altera¥15.1¥embedded

開 そ あ Embedded_Command_Shell.bat ン ン

起動

(2) ン ン 以 実行

$ export ALTERAOCLSDKROOT="C:\altera\15.1\hld" ↲

$ export PATH=${ALTERAOCLSDKROOT}/bin:$PATH ↲

$ export AOCL_BOARD_PACKAGE_ROOT=${ALTERAOCLSDKROOT}/board/c5soc_atlas ↲

(3) 現在認識 い 確認

$ cd "C:\altera\15.1\hld\bin" ↲

$ aoc --list-boards ↲

Board list:

ネ ン 4-2.

ネ ン ン Quartus Prime 開発ソ 実行 Quartus

Prime 開発ソ 起動中 あ ば終了 く い

(1) ン ン 以 ン 入力

$ cd "C:\Work\Altera-SoCFPGA-OpenCL-vectorAdd\device" ↲

$ aoc -v --report vectorAdd.cl -o vectorAdd.aocx --board c5soc_atlas_sharedonly ↲

aoc: Environment checks are completed successfully. You are now compiling the full flow!!

aoc: Selected target board c5soc_atlas_sharedonly aoc: Running OpenCL parser....

c:/Work/Altera-SoCFPGA-OpenCL-vectorAdd/device/vectorAdd.cl:23:47: warning: decl aring kernel argument with no 'restrict' may lead to low kernel performance __kernel void vectorAdd(__global const float *x,

^

c:/Work/Altera-SoCFPGA-OpenCL-vectorAdd/device/vectorAdd.cl:24:47: warning: decl aring kernel argument with no 'restrict' may lead to low kernel performance __global const float *y,

^ 2 warnings generated.

aoc: OpenCL parser completed successfully. aoc: Compiling....

aoc: Linking with IP library ...

+---+ ; Estimated Resource Usage Summary ; +---+---+ ; Resource + Usage ; +---+---+

; Logic utilization ; 65% ;

; Dedicated logic registers ; 27% ;

; Memory blocks ; 24% ;

; DSP blocks ; 0% ; +---+---; aoc: First stage compilation completed successfully.

aoc: Hardware generation completed successfully.

(2) 使用 PC ネ ン 13 分程度 ン

ン ン 表示 待

(3) ン 成 以 う vectorAdd.aocx 生成

$ ls –l ↲

合計 2276

ョン ン 4-3.

(1) ン ン 以 ン 入力

$ cd "C:\Work\Altera-SoCFPGA-OpenCL-vectorAdd" ↲

$ make all ↲

arm-linux-gnueabihf-g++ host/src/main.cpp common/src/AOCL_Utils.cpp -o vector_a dd -IC:/altera/15.1/hld/host/include -Icommon/inc -LC:\altera\15.1\hld/board/ c5soc_atlas\arm32\lib -LC:/altera/15.1/hld/host/arm32/lib -Wl,--no-as-needed -la lteracl -lalterahalmmd -lalterammdpcie -lelf -lrt -ldl -lstdc++

(2) ン 成 以 う vector_add 生成

$ ls –l ↲

合計 52

転送 4-4.

ョン ン 済 ネ Atlas-SoC microSD 転送

(1) SCP セ ュ 使用 転送

SCP 経由 PC Atlas-SoC microSD 転送 PC

scp <source_filename> root@<board_ip_address>:<target_filename> ン 使用

(2) ン ン 次 う 入力 vector_add ョン Atlas-SoC

転送 接続 続け う 聞 場合 yes ↲ 入力 例 ワ

altera.123 ↲ 使用

$ scp vector_add root@192.168.1.30:/home/root ↲

Could not create directory '/home/11149/.ssh'.

The authenticity of host '192.168.1.30 (192.168.1.30)' can't be established. ECDSA key fingerprint is SHA256:SZhkriFhnzX/arvfUwpBVVAG57AUnFXGLCSwRCnHA0E.

Are you sure you want to continue connecting (yes/no)? yes ↲

Failed to add the host to the list of known hosts (/home/11149/.ssh/known_hosts) .

Password:

vector_add 100% 42KB 42.3KB/s 00:00

(3) 次 う 入力 vectorAdd.aocx Atlas-SoC 転送 再度 ワ altera.123 ↲

使用

$ scp ./device/vectorAdd.aocx root@192.168.1.30:/home/root ↲

Could not create directory '/home/11149/.ssh'.

The authenticity of host '192.168.1.30 (192.168.1.30)' can't be established. ECDSA key fingerprint is SHA256:SZhkriFhnzX/arvfUwpBVVAG57AUnFXGLCSwRCnHA0E. Are you sure you want to continue connecting (yes/no)? yes ↲

Failed to add the host to the list of known hosts (/home/11149/.ssh/known_hosts) .

Password:

vectorAdd.aocx 100% 1663KB 1.6MB/s 00:00

Atlas-SoC microSD 転送

yes 入力

ワ 入力

ワ 入力

OpenCL 実行 4-5.

転送 ネ FPGA ン ュ ョン ョン 実行 OpenCL

動作 確認

(1) Linux ンソ 以 う 入力 Linux ュ

# source ./init_opencl.sh ↲

(2) 次のように入力 正常 動作 い 確認

# aocl diagnose ↲

aocl diagnose: Running diagnostic from /home/root/aocl-rte-15.1.0-1.arm32/board/c5soc/arm32/bin

Verified that the kernel mode driver is installed on the host machine.

Using platform: Altera SDK for OpenCL Board vendor name: Altera Corporation

Board name: DE0nanoSoc : Cyclone V SoC Development Kit

Buffer read/write test passed.

DIAGNOSTIC_PASSED

(3) 次のように入力 転送 実行可能

# chmod 777 vector_add ↲

# chmod 777 vectorAdd.aocx ↲

(4) Linux OpenCL ネ ン 行い ン ュ ョ

ン 成 LED 点滅 ン 変化

# aocl program /dev/acl0 vectorAdd.aocx ↲

aocl program: Running reprogram from /home/root/aocl-rte-15.1.0-1.arm32/board/c5soc/arm32/bin Reprogramming was successful!

(5) Linux ARM 実行

# ./vector_add ↲

Initializing OpenCL

Platform: Altera SDK for OpenCL Using 1 device(s)

c5soc_atlas_sharedonly : Cyclone V SoC Development Kit Using AOCX: vectorAdd.aocx

Reprogramming device with handle 1 Launching for device 0 (1000000 elements)

Time: 318.877 ms

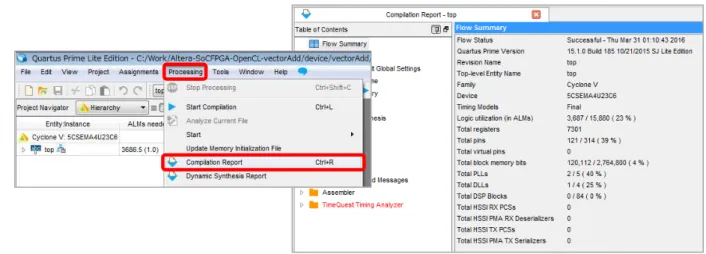

ネ ン 結果 確認 4-6.

ン ネ ン 確認

(1) Quartus Prime 開発ソ 起動 File ュ ⇒ Open Project

C:¥Work¥Altera-SoCFPGA-OpenCL-vectorAdd¥device¥vectorAdd¥top.qpf 開

図 4-6.1 Quartus Prime 開発ソ 起動 File ュ ⇒ Open Project

(2) Processing ュ ⇒ Compile Report 選択

免責 び 利用 注意

弊社 資料 入手 客様 記 使用 注意 一 い い 使用く い

1. 本資料 非売品 許可無く転売 や無断複製 禁

2. 本資料 予告 く変更 あ

3. 本資料 作成 万全 期 い 万一 不明 点や誤 記載漏 気 点 あ 本資料 入手 記代理店 一報い け ば幸い

株式会社 : http://www.altima.co.jp 術情報 EDISON: https://www.altima.jp/members/index.cfm

株式会社 セ : http://www.elsena.co.jp 術情報 ETS : https://www.elsena.co.jp/elspear/members/index.cfm

4. 本資料 取 扱 い 回路 術 関 運用 結果 影響 い 責任 負い あ 了 く い

改版履歴

Revision 年 概要